受付時間:9:00~18:00(平日)

高速バスラインは、等長配線こだわりすぎなくてよい

Before

近年、DDRメモリなどのクロックレートの上昇により、バスラインにおけるパターン配線の等長性が重視される傾向があります。小さな基板上で隣接するCPUとDRAM間のバスラインを等長で配線することは至難の業となることが多々あります。しかし、システムの動作周波数に対しどのくらいの等長性を確保したらよいのかは、あまり明確ではありません。

DDRメモリなどの高速なバス信号は、各ビットの信号遅延によるリードライトエラーを発生させないため、インピーダンスコントロールとバスラインの等長配線が重要視されます。

各バスラインの長さにおけるばらつきが数mm以下もしくはmm単位以下となるように要求があったりと、実装密度が高い基板の場合、長くなる方の配線に線長を合わせる必要があり、おのずと全体の線長が長くなり配線面積も大きくなってしまいますので、基板パターン設計にはかなりシビアな要求となります。

After

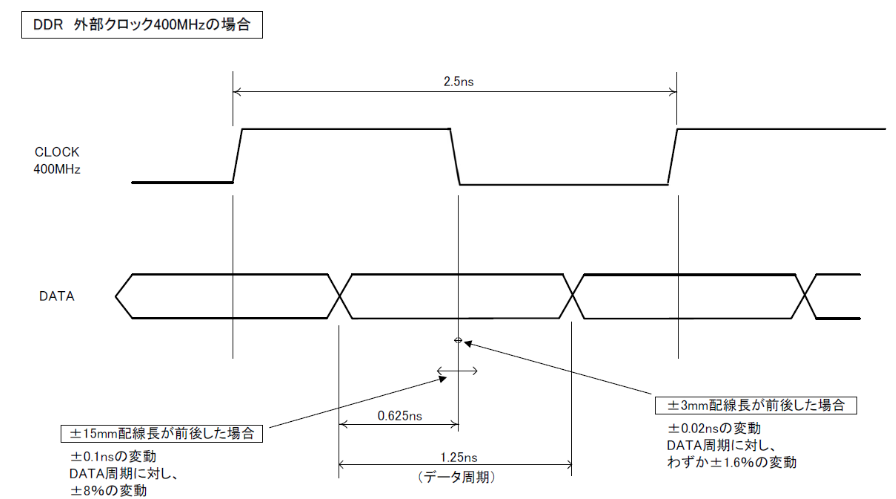

線長差による遅延を考慮すると、それほど等長配線にこだわらなくてもよいことが見えてきます。例えばDDR3-800メモリの最大バスクロックは400MHzですので、クロック周期は2.5ns、データ更新周期は1.25nsとなります。一方、基板(FR-4)表層における電気信号の伝搬遅延は、15cmでおおよそ1nsとなります。

表に示す様に、バスラインの線長差のばらつきが±3mm、±15mm(最短、最長間)とした場合、線長差による遅延のばらつきはそれぞれ±0.02ns、±0.1nsとなり、データ更新周期に対して±1.6%,±8%となります。

実際にはメモリとCPU内部の配線長やクロックのジッタなどによる取り込みタイミングのばらつきも加味されますが、この程度のばらつきは実力上問題はないと考えられます。

但し、各配線のインピーダンスコントロールは周波数が高くなるにつれて重要になってきており、各バスライン間で不整合が発生しないような注意が必要です。特に配線層を変更するためのビアの配置は、線路のインピーダンスを崩す要因となります。また、伝搬波形のシミュレーションの実施も近年比較的容易になってきているため、パターン設計時のシミュレーションを実施することを推奨します。